# A Visual Toolset for the Design of Real-Time Discrete Event Systems.

#### Jonathan S. Ostroff

Department Of Computer Science, York University<sup>1</sup>, 4700 Keele Street, North York Ontario, Canada, M3J 1P3. Email: jonathan@cs.yorku.ca Tel: 416-736-2100 X77882 Fax: 416-736-5872

Abstract: StateTime is a prototype toolset that supports the design of verified real-time discrete event systems using executable visual state descriptions (the Build tool). Visual state descriptions allow the designer to browse and understand the structure of the system. A timing hierarchy of spontaneous, just and forced timed events, and a variety of computational notions such as concurrency, hierarchy, nondeterminism, process interaction and communication can be represented. The combination of model-checking (the Verify tool) and theorem proving allows for the treatment of finite and infinite state systems. The toolset is illustrated with a shutdown controller of a reactor, as taken from an actual industrial requirements document in which the system is described informally using a mixture of English descriptions, timing diagrams and pseudocode. Using StateTime, a unified precise description of the shutdown reactor is obtained, which can then be checked automatically for conformance with its requirements.

**Keywords**: real-time discrete event systems, verification tools, real-time temporal logic, timed transition models, visual descriptions.

<sup>1.</sup> This work is supported in part by the National Science and Engineering Council of Canada. This work is scheduled to appear in *IEEE Trans. on Control Systems Technology*, May 1997.

## **Table of Contents**

| 1.0 | Intro                                           | duction                                        | 3  |

|-----|-------------------------------------------------|------------------------------------------------|----|

| 2.0 | Exan                                            | nple — nuclear reactor shutdown system         | 4  |

| 3.0 | The T                                           | ГТМ/RTTL framework                             | 7  |

|     | 3.1                                             | Timed Transition Models (TTMs)                 | 7  |

|     | 3.2                                             | Real-Time Temporal Logic (RTTL)                | 10 |

|     | 3.3                                             | TTM semantics (computations and trajectories)  | 12 |

| 4.0 | Over                                            | view of the StateTime toolset                  |    |

| 5.0 | Analysis and design of the delayed reactor trip |                                                | 16 |

|     | 5.1                                             | Using the Build tool to describe the DRT plant |    |

|     | 5.2                                             | The DRT requirements                           | 21 |

|     | 5.3                                             | The DRT controller                             |    |

|     | 5.4                                             | Checking conformance                           |    |

| 6.0 | Comj                                            | parison of StateTime to other tools            | 27 |

| 7.0 | Conc                                            | lusions                                        | 31 |

| 8.0 | Refer                                           | rences                                         | 32 |

# Figures

| Analog implementation of the delay relay trip timing           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Faulty pseudocode for the computer to control the DRT          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A sample computation of the air bag system                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| StateTime checks that a TTM conforms to its RTTL specification | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The TTMchart of the system under design (edit view)            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Connection diagram for the system under design                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TTMchart description of the DRT plant                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Main window of the Build tool                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Hierarchy of plant objects                                     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Simulating the plant produces a computation                    | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Corrected pseudocode for the computer to control the DRT       | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Result of transforming the controller pseudocode into a TTM    | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Abbreviated output from the Verify tool for requirement [R2]   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Observer to check requirement R1                               | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Abbreviated view of a counterexample                           | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

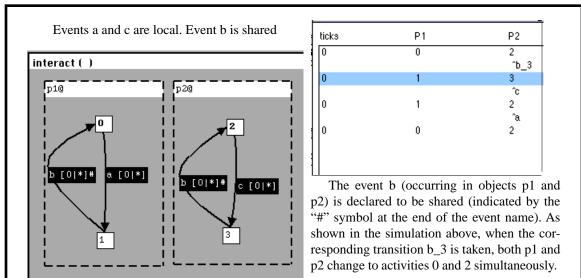

| Shared transitions allow objects to synchronize                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | Analog implementation of the delay relay trip timing<br>Faulty pseudocode for the computer to control the DRT<br>A sample computation of the air bag system<br>StateTime checks that a TTM conforms to its RTTL specification<br>The TTMchart of the system under design (edit view)<br>Connection diagram for the system under design<br>TTMchart description of the DRT plant<br>Main window of the Build tool<br>Hierarchy of plant objects<br>Simulating the plant produces a computation<br>Corrected pseudocode for the computer to control the DRT<br>Result of transforming the controller pseudocode into a TTM.<br>Abbreviated output from the Verify tool for requirement [R2]<br>Observer to check requirement R1<br>Abbreviated view of a counterexample<br>Shared transitions allow objects to synchronize |

## **1.0 Introduction**

Computers are increasingly used to monitor and control *reactive* safety critical systems. Real-time software in such computers controls aircraft, shuts down nuclear power reactors in emergencies, keeps telephone networks running, and monitors hospital patients. The use of computers in reactive systems offers considerable benefits, but also poses serious risks to life and the environment [35].

Reactive software is more realistically modelled by asynchronous discrete event theories than by continuous differential or synchronous difference equations. The complexity of reactive systems necessitates viewing them at different levels of abstraction. A high-level view of these systems will often involve discrete control actions, tasks, switching between modes and logical decision making. Many problems in reactive systems may be inherently discrete in nature (e.g. scheduling of control tasks).

The need for rigorous means of ensuring logical correctness of complex reactive systems, has given rise to diverse approaches by control theorists<sup>2</sup> on the one hand (e.g. the Ramadge-Wonham theory of discrete event systems [43,45]), and computer scientists on the other (e.g. process algebras [19], extended transition systems [9], and temporal logic [31]).

Control theorists developed various synthesis techniques for discrete event systems [5,12,13,20,28]. Most of the early work in synthesis was set in the simple framework of finite automata, with more recent extensions to real-time and infinite-string formal languages leading to the solution of some problems of realistic complexity [45]. However, actual industrial reactive systems need the representational advantages of real-time programming languages such as Ada and Occam (e.g. assignments to typed data variables and scheduling features).

In the more complex domain of typed variables and programming constructs, synthesis results are harder to come by. For example, the overall problem of program verification, including that of the synthesis of invariant assertions is undecidable [29].

In this paper we consider the TTM/RTTL framework for the design and analysis of discrete real-time reactive systems. The TTM/RTTL framework [32,33,40] consists of the following components:

• A *constructive description language* called timed transition models (TTMs) for describing reactive systems. A TTM is a guarded transition system with lower and upper bounds on the transitions that relate to the occurrence of a special transition *tick*. Concurrent real-time programs, nondeterministic timed Petri nets and diverse mechanisms for timing, synchronization and communication constructs can be converted into TTMs in a straightforward manner.

<sup>2.</sup> We focus on those theories that adapt the ideas of classical control theory to the synthesis of supervisory controllers for discrete event systems. There is another important stream associated with the performance analysis, simulation and optimization of discrete event systems (e.g. see [7,8]); this stream is not discussed in the sequel.

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

- A *declarative specification language* called real-time temporal logic (RTTL) for describing the requirements that a TTM should satisfy without discussing how the TTM is constructed. RTTL is a timed extension of linear temporal logic, augmented with clock and event variables.

- Analysis techniques for demonstrating that a TTM conforms to its specification. A proof system for theorem proving and model-checking are the main analysis techniques. Model-checking is a method of automatically verifying concurrent systems in which a finite-state model of the system (TTM) is compared with a correctness requirement (RTTL). Since time is a monotonically increasing variable, the state-space of naive timed systems is automatically infinite state. Hence, model-checking algorithms need special care to ensure that the system remains finite state.

## Purpose of this paper

The purpose of this paper is to describe the *StateTime* toolset for design and analysis of real-time reactive systems within the TTM/RTTL framework. To convey how the various parts of StateTime are used as a unified tool for analysis and design, we provide a complete development example taken from the shutdown system for a nuclear plant, as taken from an actual industrial requirements document in which the system is described using a mixture of informal English language descriptions, timing diagrams and pseudocode (Section 2.0). Using StateTime, a precise visual description of the shutdown reactor is obtained, which can then be checked automatically for conformance with its requirements (Section 5.0).

StateTime has a visual description language with richer automated verification techniques for real-time systems than a commercially available visual tool. We compare StateTime to other tools in Section 6.0. The visual state descriptions allow the designer to browse and understand system structures.

## Organization of the rest of this paper

Section 2 presents the informal descriptions and requirements of the reactor shutdown system in order to illustrate the type of problem StateTime is intended to be used on. Section 3 describes the TTM/RTTL framework. Section 4 presents the various features and tools of StateTime. Section 5 applies the toolset to the design and analysis of the shutdown system. In Section 6, StateTime is compared to other tools (especially Statemate). Conclusions and future work are discussed in Section 7.

Readers unfamiliar with formal logic and verification may want to skip Sections 3 and 4 on a first reading to obtain a working understanding of StateTime before looking at the underlying details.

# 2.0 Example — nuclear reactor shutdown system

In early nuclear reactors, the shutdown systems were constructed of analog devices. The analog control had the virtue of being simple to understand but inflexible, unable to perform system checks and not always reliable. It was felt that the situation could be improved by installing computerized control with at least two independent shutdown systems, designed by different teams, each shutdown system itself having 3-version control and majority voting logic [41].

The delayed reactor trip (DRT) problem was first described by Lawford *et. al.* [25]. Lawford developed behaviour preserving transformations for timed transition models (TTMs) with which he was able to discover a flaw in the proposed design [24]. However, his theory cannot be automated as no set of transformations is complete for proving observation equivalence between the actual implementation and its abstract specification. In the sequel we will use the StateTime tool to describe the DRT and automatically check that it conforms to its requirements.

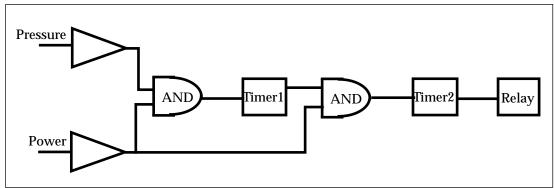

The DRT for nuclear reactors used to be implemented in hardware using timers, comparators and logic gates similar to the diagram shown in Figure 1. The

new DRT system is implemented on microprocessors. Digital control systems provide cost savings and flexibility over the hardware implementation. However, the question now is whether the new microprocessor based software controller satisfies the same specifications as the old hardware implementation.

The hardware version of the controller implements the following informal requirements:

**[R1]** When the power and pressure of the reactor exceed acceptable safety limits, the comparators which feed in to the first AND gate cause Timer1 to start, which times out after 3 seconds and sends a message to one of the inputs of the second AND gate indicating that the time-out has occurred. If after this first time-out the power is still greater than its safety limit, then the relay is tripped (opened), and Timer2 starts. The relay must remain open until Timer2 times out which happens after 2 seconds.

Requirement [R1] ensures that the relay is opened and remains open for two seconds thus shutting down the nuclear reactor in a timely fashion. If the controller fails to shut down the reactor properly, then catastrophic results might follow including danger to life. Conversely, each time the reactor is improperly shut down, the utility operating the reactor loses money because it must bring additional fossil fuel generating stations on line to meet demand. The next informal requirement states:

**[R2]** If the power reduces to an acceptable level then the relay should be closed as soon as possible (thus allowing the reactor to operate once more).

A final requirement that is *implicit* in the hardware specification, but must be *explicitly* stated for the software version is:

[R3] The controller should never deadlock.

For example, if after the power and pressure have exceeded their critical values, and the computer has waited 3 seconds to check the power level again, if the power is below its critical limit, then the computer should reset and go back to monitoring its inputs (failure to do so would result in a deadlock).

In the actual DRT, there are three identical systems running in parallel with the final decision on when to shut down the reactor implemented on a majority rule basis. In this section we analyze a closed system consisting of the plant (relay, power and pressure) and a single microprocessor controller. The 3-version system can also be verified using the techniques discussed in this paper and compositional reasoning [38].

The original requirements document, taken from an actual industrial example, provided the pseudocode in Figure 2 as the specification for the controller. This

| Every one tick of the clock Do:<br>If P=1 {pressure is high} |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| then                                                         | If W=1 {power is high} then<br>If counter Ta is reset then<br>If Tb is reset then<br>increment Ta<br>EndIf<br>Else<br>If counter Tb has timed out then<br>reset Tb<br>Else<br>increment Tb<br>open Relay<br>Endif<br>Else<br>If counter Ta has timed out then<br>open Relay<br>reset Ta<br>increment Tb<br>Else<br>Else<br>increment Tb<br>Else<br>If counter Ta has timed out then<br>open Relay<br>reset Ta<br>increment Tb<br>Else<br>increment Tb | else | If counter Ta is reset then<br>If counter Tb is reset then<br>close Relay<br>Else<br>If counter Tb has timed out then<br>close Relay ; reset Tb<br>Else<br>increment Tb<br>open Relay<br>Endif<br>Endif<br>Else<br>If counter Ta has timed out then<br>reset Ta<br>Else<br>increment Ta<br>Else<br>Else<br>increment Ta |

FIGURE 2. Faulty pseudocode for the computer to control the DRT

code was to be implemented on a microprocessor with a cycle time of 100ms. The microprocessor samples the inputs (pressure and power) and passes through a block of code every 0.1 seconds. It is assumed that the input signals have been

properly filtered and that the sampling rate is sufficient to ensure adequate control. In the formal model, one tick of the clock will represent 100ms. The pseudocode makes use of two integer counters *Ta* and *Tb* for the two time-outs of 30 and 20 clock ticks respectively.

# 3.0 The TTM/RTTL framework

## 3.1 Timed Transition Models (TTMs)

TTMs are timed extensions of fair transition systems of Manna and Pnueli [31]. Transitions have lower and upper time bounds that refer to the number of occurrences of a special transition *tick* in a computation of a system. A TTM *M* is defined as a 4-tuple M = (V, I, T, J) as follows:

- V: a finite set of typed *system variables*. There are two distinguished variables that are always elements of V: the discrete clock time t and the event variable ε. The *clock time* t ∈ V has type(t) = {0, 1, 2, ...∞}. The event variable indicates what transition has just been taken; its type is the transition set (see below). There may also be *data variables* which range over data domains such as integers, rationals, lists or sets. *Object variables* (also called control variables) are used to indicate progress in the execution of the various concurrent threads or processes of the TTM. A state *s* of the TTM is a mapping that assigns to each variable *v* ∈ V a value in *type(v)*. For example, if the system variables are V = {*t*, ε, *b*, *r*} where *b* is a boolean and *r* is rational variable, then the state *s* = ⟨*t*:10, ε:tick, *b*:true, *r*:6.8⟩ denotes a system state after taking a clock tick at time *t* = 9. The set of all states is denoted by Σ.

- *I*: the *initial condition*. This is a satisfiable boolean valued expression in the system variables that characterizes the states at which the execution of the TTM can begin. A state *s* satisfying *I* (written  $s \models I$ ) is called an *initial state*.

- *T*: a finite *set of transitions* which includes the distinguished transitions *initial* and *tick*. Each transition  $\tau \in T$  is a function  $\tau: \Sigma \rightarrow powerset(\Sigma)$  that maps a *prestate s* in  $\Sigma$  to a (possibly empty) set of  $\tau$ -successor states  $\tau(s) \subseteq \Sigma$ . The successor states are also called the *poststates* of  $\tau$  and *s*.

- *J*: a *justice set* where  $J \subset T$ . Informally, the justice constraint for each transition  $\tau \in J$  disallows computations in which  $\tau$  is continually enabled but not taken beyond a certain point<sup>3</sup>. The *tick* transition is always in the justice set.

It is convenient to represent the effect of taking a transition by a *transition relation* which is a first order formula  $\rho_{\tau}(V, V')$  that relates a *prestate s* to any of its poststates  $s' \in \tau(s)$ . The transition relation refers to both unprimed and primed system variables. An unprimed variable v is evaluated in the prestate s while the corre-

<sup>3.</sup> Justice (weak fairness) is defined more formally later. We may also allow a set of *compassionate* transitions (strong fairness). Compassionate transitions are not used in the examples of the sequel. The StateTime tool supports both just and compassionate transitions. See [31] for a precise definition of compassion.

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

sponding primed variable *v*' is evaluated in the poststate *s*'. Assuming  $V = \{t, \varepsilon, b, r, y\}$ , the tick transition relation is:

$$\rho_{tick}(V, V')$$

:  $(t' = t + 1) \land (\varepsilon' = tick) \land same(b, r, y)$

where  $same(b, r, y) \equiv [(b = b') \land (r = r') \land (y = y')]$ , i.e. the variables *b*, *r* and *y* remain unchanged when the tick transition is taken. The only variables that change are the global time *t* (which is incremented by one), and the event variable  $\varepsilon$  which is updated to indicate which transition has just been taken. All other variables remain the same. Any non-tick transition leaves the clock unchanged. An example of a non-tick transition relation (e.g. for transition  $\alpha$ ) is:

$$\rho_{\alpha}(V, V') : (r' = r + y) \land (r \ge y) \land (\varepsilon' = \alpha) \land same(t, y)$$

(Eq 1)

The clock variable *t* remains the same when  $\alpha$  is taken. The conjunct  $(r \ge y)$  in the unprimed variables in (Eq. 1) is the *enabling condition*  $enb(\alpha)$  of transition  $\alpha$ , i.e.  $\alpha$  can only be taken if *r* is at least as large as *y* in the prestate. The simultaneous *update function*  $upd(\alpha) = \{e: \alpha, r: r + y\}$  is used to denote those variables that change when the transition is taken<sup>4</sup>.

The enabling condition  $enb(\tau)$  of transition  $\tau$  can be formally defined from its transition relation by  $enb(\tau) \equiv (\exists V' | \rho_{\tau}(V, V'))$ . We say that transition  $\tau$  is *enabled* in a state s (written:  $s \models enb(\tau)$ ) if  $\tau(s) \neq \emptyset$  — otherwise  $\tau$  is said to be *disabled*.

In the sequel, we often describe a transition  $\tau$  by its enabling condition  $enb(\tau)$  and update function  $upd(\tau) = \{v_1: e_1, v_2: e_2\}$ , where  $e_1$  and  $e_2$  are expressions in the system variables. The corresponding transition relation is given by  $\rho_{\tau}(V, V')$ :  $enb(\tau) \wedge (v_1' = e_1) \wedge (v_2' = e_2)$ .

In general, formulas such as the enabling condition and initial condition are called *state-formulas*, i.e. predicates in the unprimed system variables. State-formulas can be evaluated to true or false given a single state; hence the notation  $s \models f$  for a state-formula *f*. Transition relations require two states (the prestate and poststate) for their evaluation. Temporal logic formulas (see next section) require sequences of states (called computations) for their evaluation.

In addition to the enabling condition and update function associated with each transition, each non-tick transition  $\tau$  also has an associated lower time bound  $low(\tau)$  and upper time bound  $up(\tau)$ , where  $0 \le low(\tau) \le up(\tau) \le \infty$ .

A timed transition  $\tau[l, u]$  with lower time bound *l* ticks and upper time bound *u* ticks, must delay *l* ticks before being taken, but must be taken by *u* ticks of the clock, unless it is pre-empted by some other transition. In increasing order of timing stringency we have:

A spontaneous transition τ[0, ∞] may occur at any point in time after becoming enabled, or it may never occur. For example, a device failure is spontaneous. In the sequel, a spontaneous transition is indicated by the fact that its upper time bound is infinity (∞).

<sup>4.</sup> The variables that are unchanged are by convention not included in the update function.

- *A just transition* must eventually occur if it is continually enabled. For example, a process that is continuously enabled to enter its critical region should eventually be allowed in. Justice is qualitative in the sense that although a just transition must occur, no finite bound on the time of occurrence is given.

- *A timed transition* such as τ[3, 7] must occur within an interval specified by a lower and an upper time bound. For example, sending a message may take between 3 and 7 ticks of the clock.

It is possible to have examples of all three types of transitions in a single TTM. When modelling a system, we can initially make all transitions spontaneous. As more timing information becomes available we can add justice constraints or tighten the bounds to provide a more precise description of the system behaviour.

In the next subsection, we provide the formal operational semantics of a TTM by describing its computations. Informally, a computation starts in an initial state. From any state of the computation, any enabled transitions is taken *in one atomic step*. The resulting interleaving of enabled transitions allows us to model concurrent processes<sup>5</sup>. When the transitions are taken, they update the variables according to the transition relation. The clock must tick infinitely often in any computation, and an arbitrary but finite number of (non-tick) transitions can be taken between any two ticks of the clock. The lower and upper time bounds of transitions must be respected, e.g. a lower bound of 3 requires that the transition not be taken for 3 clock ticks (even though the transition is enabled).

There are three sources of non-determinism in TTMs. (a) The transition relation itself may be non-deterministic. (b) Even if all transition relations are deterministic, many transitions may be enabled in the same state, and hence at any moment only one is nondeterministically taken. (c) Timing intervals introduce nondeterminism. Even a transition with an exact discrete delay (e.g.  $\tau[3,3]$ ) allows  $\tau$  to be taken in any state after the 3rd but before the 4th tick of the clock from the moment the transition became enabled. Case (c) corresponds to asynchronous systems in which many actual events can occur sequentially between two ticks of the computer clock. In synchronous systems, all enabled transitions are taken simultaneously, and are thus based on the assumption that the environment does not interfere with the program during reactions [4].

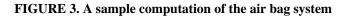

As an asynchronous discrete example, consider a computer that checks all sensors in an automobile every 30 milliseconds (one tick = 30ms.). The air bag is one of the safety devices monitored by the computer. Impact is registered by a sensing device in the front of the car. The electronic circuit monitoring the sensor signals a solid propellant inflator to begin the chemical reaction that generates nitrogen gas to start filling the air bags. The air bag is fully inflated at 55 ms. The observed computation is provided in Figure 3.

As far as the discrete computer is concerned, the impact and start of the air bag expansion are in the same time interval [T,T+30) between the 7th and 8th clock

<sup>5.</sup> Actual systems may have *overlapped* rather than interleaved execution. However, provided an appropriate just set of transitions with the right level of atomicity is chosen, the interleaving model can accurately describe overlapped execution (see [31, p103] for further discussion).

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

tick, but causally ordered within that interval (*startBag* is after *impact*). The computer cannot record that full inflation of the bag occurs at precisely 55ms., only that it is in the second interval [T+30,T+60]. The decision to keep time discrete is often a reasonable assumption as any computer runs to some digital clock cycle, and hence cannot discriminate to a finer timestamp than its basic cycle. The computation in Figure 3 is written more compactly as:

$\langle initial, s_0 \rangle \dots \langle tick, s_{11} \rangle \langle impact, s_{12} \rangle \langle startBag, s_{13} \rangle \langle tick, s_{14} \rangle \langle inflated, s_{15} \rangle \dots$

If the transition information is unimportant we write the computation as  $s_0s_1s_2s_3...$

The event variable may be used to describe the occurrence of transitions. For example, the state-formula ( $\varepsilon = impact \land t \ge 7$ ) is true in state  $s_{12}$  but false in  $s_{13}$ . We refer to state  $s_i$  as *position i* in the computation. The initial state is always position zero.

## 3.2 Real-Time Temporal Logic (RTTL).

Linear time temporal logic [31] uses temporal connectives such as  $\Box$  (henceforth),  $\diamond$  (eventually) and  $\mathfrak{A}$  (until) to represent quantitative temporal properties. The standard connectives are applied to state-formulas to obtain temporal logic formulas. Temporal logic formulas may be interpreted with respect to a computation, e.g.

- $\diamond((\epsilon = inflated) \land t = 8)$ : there is some position, 8 ticks after the initial position of the computation, in which the air bag has been inflated. The computation in Figure 3 satisfies this temporal property, since the state  $s_{15}$  is a reachable state satisfying (( $\epsilon = inflated$ )  $\land t = 8$ ).

- $(\varepsilon = impact \land t = 7) \rightarrow \Diamond(\varepsilon = inflated \land t = 7)$ : if in the initial position of the computation there is an impact at time t = 7, then prior to any further ticks, there is a subsequent position in which the air bag is fully inflated. This property is paradoxically true in the computation of Figure 3, because the antecedent  $(\varepsilon = impact \land t = 7)$  is false in the initial position.

•  $\Box[(\varepsilon = impact \land t = 7) \rightarrow \Diamond(\varepsilon = inflated \land t = 8)]$ : if in *any* position of the computation there is an impact at clock time t = 7, then there must be a subsequent state, one tick later, in which the air bag is fully inflated.

We use the *entails* operator  $(\Rightarrow)$  for expressing response properties. The entails operator is defined as:  $[p \Rightarrow \Diamond q] \equiv \Box [p \rightarrow \Diamond q]$ . The property  $p \Rightarrow \Diamond q$  is pronounced *p entails* eventually *q*. Implication  $(p \rightarrow \Diamond q)$  states only that *p* implies eventually *q* at the initial position of the computation. Entailment  $(p \Rightarrow \Diamond q)$  states that the implication holds at *all* positions of the computation.

- $\Box \diamondsuit (\varepsilon = tick)$ : every position in the computation is eventually followed by a position at which the clock has just ticked, i.e. the clock ticks infinitely often. This property holds on computations that are *infinite* sequences of states.

- $p\mathfrak{A}_q$ : *p* until *q*, i.e. *p* is true in all positions up to but not including *q*. The property  $p\mathfrak{W}_q$  (*p* waiting-for *q*) can be defined as:  $(p\mathfrak{A}_q) \vee \Box p$ .

We refer the reader to [31] for a complete exposition of linear temporal logic. The logic allows for the use of flexible and rigid variables. The system variables in *V* are called *flexible variables* as they change from state to state. *Rigid variables* remain the same throughout a computation (e.g.  $\top$  in Figure 3).

We will call the standard formulas of temporal logic (that have no occurrences of the clock variable *t*) *unclocked* properties. Real-time temporal logic (RTTL) includes standard temporal logic, but also allows references to the clock time *t* and additional rigid timing variables. We will call these additional timing properties *clocked* formulas.

Most proposals for *real-time* temporal logics extend the standard operators with new connectives such as  $\diamond_{\leq 5} p$  (before the 6th ticks of the clock p holds) or use special clock variables [1]. Thus the bounded response property  $p \Rightarrow \diamond_{\leq 5} q$  asserts that every occurrence of a p-state is followed within 5 clock ticks by a q-state (a state satisfying q).

In our framework there is no need to introduce new temporal operators. By using standard unextended temporal logic, we can re-use many of the tools and methods developed for untimed systems. For example, the definition of the bounded response property is [32]:

$$\diamondsuit_{[4, 6]}q: [\forall t_0 | ((t = t_0) \rightarrow \diamondsuit(q \land (t_0 + 4 \le t < t_0 + 6)))]$$

(Eq 2)

The response property is universally quantified over the rigid variable  $t_0$  which has the same type as the clock variable t. The above response property states that if the clock variable has the value  $t_0$  in the initial position of the computation, then there must be a subsequent position in which q is true, which occurs after the 4th but before the 7th tick of the clock from the initial position.

By (Eq. 2),  $p \Rightarrow \diamondsuit_{\leq 5}q$  is an abbreviation for  $p \Rightarrow \diamondsuit_{[0, 5]}q$ , and  $p \Rightarrow \diamondsuit_{8}q$  is an abbreviation for  $p \Rightarrow \diamondsuit_{[8, 8]}q$  (i.e. every *p*-state is followed precisely 8 ticks later by a *q*-state). Additional timed operators can be defined. For example,  $\Box_{<5}p$  means that *p* is true from the initial position until the position just before the 5th tick of the clock.

Given a computation  $\sigma = s_0 s_1 s_2 s_3 \dots$  and a temporal logic formula *p* we write  $\sigma \models p$  if  $\sigma$  satisfies *p*. We write  $M \models p$  when *p* is satisfied in all computations of the TTM *M*. If *p* is a state-formula, then  $[\sigma \models p] \equiv [s_0 \models p]$ .

## 3.3 TTM semantics (computations and trajectories)

A computation  $\langle initial, s_0 \rangle$ ,  $\langle \tau_1, s_1 \rangle$ ,  $\langle \tau_2, s_2 \rangle$ , ... of a TTM M = (V, I, T, J), where  $\tau_i \in T$  for  $i \ge 1$ , is an infinite sequence of states satisfying the following three constraints:

- 1. *Initialization*: The first state of the computation satisfies the initial condition<sup>6</sup>, i.e.  $s_0 \models (I \land (\varepsilon = initial))$ .

- 2. *Succession*:  $(\forall i | i \ge 1: s_{i+1} \in \tau_{i+1}(s_i))$ , i.e. every prestate at position *i* must have as its successor a poststate according to the transition relation of  $\tau_{i+1}$  (the transition taken at position *i*).

It follows from succession that  $s_i \models (enb(\tau_{i+1}) \land (\varepsilon = \tau_i))$ .

3. *Justice*: For each transition  $\tau$  in the justice set, it is not the case that  $\tau$  is continually enabled beyond some position in the trajectory, but taken at only finitely many positions in the trajectory.

The above three constraints are the standard description of fair transition systems [31], to which we have added the event variable  $\varepsilon$ , for descriptions that involve both state and transition information.

A *trajectory* is a computation that is further constrained by the lower and upper time bounds of transitions, defined as follows:

- 4. *Ticking*: The clock ticks infinitely often in the computation, i.e.  $\Box \diamondsuit (\varepsilon = tick)$ .

- 5. *Lower bound*: for every transition  $\tau$  with lower bound l > 0, if  $\tau$  is taken at position j of the computation, then there must exist a prior position  $i \le j$  so that  $s_i(t) + l \le s_j(t)$  and  $(\forall k | i \le k \le j: s_k \Vdash enb(\tau) \land \varepsilon \ne \tau)$ , i.e.  $\tau$  is enabled but not taken in the states  $s_i \dots s_j$ .

- 6. *Upper bound*: for every transition  $\tau$  with upper bound  $u \neq \infty$ , if  $\tau$  is enabled at position *j* of the computation, then there must exists a subsequent position  $k \ge j$  with  $s_j(t) + u \ge s_k(t)$ , such that either  $\tau$  is taken or disabled at position *k*.

Once a transition  $\tau$  becomes enabled at position *i*, it begins to "mature" but cannot be taken until its lower time bound number of ticks has been taken, at which point the transition becomes "ripe" for execution. If the transition is continuously enabled during maturation, then it can be taken any time after it becomes ripe, but it must be taken or become disabled before the upper time bound number of ticks has expired. Thus, transitions "mature" together as time advances but execute separately in an interleaving manner.

<sup>6.</sup> The transition *initial* occurs once at the beginning of the computation and never again.

Unfortunately, not every TTM is guaranteed to satisfy both the ticking and the time bound requirements. If there is any *immediate* transition  $\tau[0,0]$  that is a self-loop, then  $\tau$  is taken an infinite number of times before a tick transition. This is called a *Zeno computation*. Any cycle whose elements are all immediate may also create Zeno computations.

The problem of Zeno computations can be avoided by disallowing self-looping immediate transitions. However, immediate transitions are useful for modelling "instantaneous" (i.e. before the clock ticks) reactions. If immediate transitions are used in a TTM *M*, then the we must check for the validity of  $M \models \Box \diamondsuit (\varepsilon = \tau)$ . Fortunately, for those systems where model-checking can be used (e.g. finite state systems), the ticking property can be verified automatically. Alternatively, suppose it is suspected that the TTM *M* may have Zeno behaviour. Then, to check that *M* satisfies the temporal logic requirement *r*, verify that  $M \models (\Box \diamondsuit (\varepsilon = \tau) \rightarrow r)$ , i.e. *r* is satisfied in every non-Zeno path.

The model of TTMs presented above is expressive enough to capture most of the features specific to real time programs including delays, time-outs, preemptions and interrupts. See [32] for the use of TTMs to model the constructs of the real-time Ada-like language Conic.

## 4.0 Overview of the StateTime toolset

Engineers seek ways to describe and analyze their designs, whether these designs involve circuits, fluid flow in pipes, or the deformation of a beam. The purpose of the Statetime toolset is to support visual descriptions of discrete realtime reactive systems, including program components.

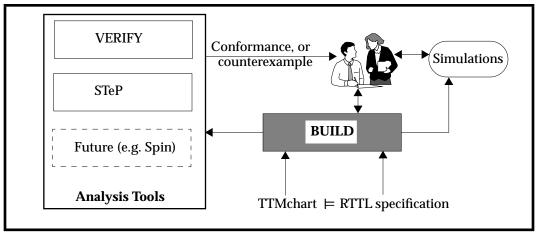

The toolset assists the user to (a) describe devices and systems diagrammatically, (b) execute the description so as to validate that the description is a reasonable model of the actual system, and (c) check that the description conforms to its requirements (e.g. the absence of deadlock or bounded response) using modelchecking and theorem proving. The TTM/RTTL framework provides the underlying mathematical basis for describing and analyzing systems. Figure 4 shows the various parts of StateTime. The *Build* tool is a window-based front end for

FIGURE 4. StateTime checks that a TTM conforms to its RTTL specification

constructing visual models called TTMcharts. TTMcharts resemble statecharts, but with a simpler semantics and with the additional feature that transitions may have time bounds. We often use the terms TTMcharts, charts and TTMs interchangeably.

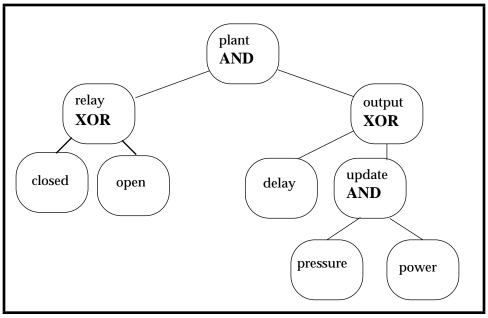

A chart is a hierarchy of objects<sup>7</sup>, which in turn are composed of sub-objects, down to basic objects (which are control states called *activities*). The objects can be related by one of two relations:

- 1. "AND" which means that they act (and interact) in parallel, or

- 2. "XOR" which means that only one of them is active at a time (i.e. they form a transition system, so that one may have multi-level transitions from one XOR object to another).

Objects have variables which are tested and set by transitions.

An engineer can describe systems incrementally by composing objects together to form more complex objects (bottom up), or by decomposing an object which is an abstraction of a component into further sub-objects (top down). A chart can be executed (or simulated) at any point in the development cycle even before it is finally fixed. The simulation tool displays various computations or trajectories of the chart.

The Build tool automatically translates charts into a TTM. The main advantage of this translation is that the chart can be automatically analyzed for conformance with its requirements. If the chart is translated into a timed transition model M that is required to satisfy RTTL properties  $r_1, r_2, r_3$ , then *conformance* means that  $M \models (r_1 \land r_2 \land r_3)$  holds. The main analysis techniques are model-checking and theorem proving. Build is written in Smalltalk, which allows it to run on most platforms (Unix, Windows and Apple Macintosh).

Model-checking supports routine automated analysis of systems but is subject to the problem of combinatorial explosion of states, i.e. the system must be reducible to a few million states (or nodes if symbolic techniques are used). Theorem proving can deal with large or infinite state systems and systems with unspecified timing parameters; but interactive guidance from the user is then required.

For simplicity, we limit the discussion in the sequel to model-checking. However, the StateTime tool supports theorem proving using constraint logic [32,34].

The *Verify* tool [33,36] was the first model-checker for a subset of real-time temporal logic. It explicitly enumerates the global state reachability graph of any finite state TTM using the algorithm reported in [33], and then checks that the chart satisfies requirements specified as formulas of real-time temporal logic. Since states are enumerated explicitly, the tool is much slower than current symbolic techniques (Verify is written in Prolog whereas modern model-checkers are written in C). In the worst case, it generates a number of states proportional to the product of the upper time bounds of all the transitions (see discussion below).

<sup>7.</sup> The term "object" describes an entity with persistent state; it is not used in the sense of objected-oriented programming.

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

Although there are now more efficient tools that can be used (Section 6.0), Verify has one feature not found in other tools. When it checks response properties such as  $p \Rightarrow \diamondsuit_{[l, u]} q$ , the time bounds [l, u] are left unspecified so that the tool finds the values for which the property is verified. If the property is unsatisfied for any finite upper bound, then a counterexample of the failing computation is provided.

The ability to leave bounds unspecified is useful. Experience dealing with actual systems continually shows that the putative specification one imagines to be true usually does not hold, particularly when it comes to timing. It is thus vital to have a tool that tells you for which bounds the property does hold. As parameters of the chart are adjusted, the engineer can continually calculate improvements in the bounds using this feature.

A recent addition to the StateTime tool is a translator from TTMcharts to the fair transition systems of STeP [30] using the algorithm presented in [39]. This algorithm can also be used in the future to produce translators from TTMs to other third party symbolic tools such as Spin [21]. STeP is the only available tool for checking linear temporal logic with past operators, and it also has good theorem proving facilities.

The translation to STeP allows for the following:

- Any unclocked property can be checked automatically.

- Clocked properties can also be checked automatically using the distinguished tick transition as a counter. For example, to check the clocked property *p* ⇒ ◊<sub>[1,1]</sub>*q* we may check the equivalent unclocked property:

$$p \Rightarrow (\varepsilon \neq tick) \mathcal{U}(\varepsilon = tick \land (\varepsilon \neq tick \mathcal{U}q))$$

(Eq 3)

Since the model-checker is exponential in the size of the formula, this approach is impractical for large time bounds.

- For clocked properties involving large time bounds we use Verify where possible. Alternatively, these properties can be rewritten in terms of additional clock variables (as in [1]).

- Another possibility for checking clocked properties is by constructing an *observer* that detects violations of the timing properties. The latter approach increases the size of the reachability graph but decreases the size of the temporal logic formula that must be checked. This is a good trade-off as the model-checking algorithm for linear temporal logic is of order

$$|M| \cdot e^{|r|} \tag{Eq 4}$$

where |M| is the size of the reachability graph and |r| is the size of the temporal logic formula to be checked. The observer approach will be illustrated in the sequel.

• Finally, STeP can model-check certain infinite state systems as it does system reduction before applying the model-checker.

When computing conformance, we use Verify for obtaining the bounds of response properties, and STeP for unclocked properties (Section 5.4). Both tools provide counterexamples which are computations in which the property fails to

hold. Counterexamples together with the simulation tool are helpful for debugging the design.

For Verify and STeP, the size of the reachability graph |M| in (Eq. 4) can in the worst case be of order  $m \cdot u$ , where m is the number of states in the untimed reachability graph (all lower bounds zero and all upper time bounds infinity), and u is the product of all the upper time bounds. This theoretical limit is usually not reached for Verify because it has a heuristic for grouping together multiple ticks of the clock [33]. The heuristic works best when all the transitions have non-zero lower time bounds, and sometimes provides insensitivity to the magnitude of the upper time bounds.

# 5.0 Analysis and design of the delayed reactor trip

The informal description of the DRT (Section 2.0), which is taken from an actual requirements document, uses a mixture of timing diagrams, pseudocode and English language descriptions. In order to use the StateTime tool we must proceed in a disciplined fashion, distinguishing between *descriptions* of what already exists (by using TTMs), and *requirements* that specify what should be (by using RTTL).

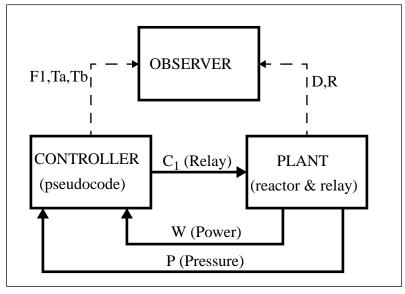

For the DRT, the complete system under description (*sud*) is the parallel composition of the *plant* (relay, pressure and power sensors) and the *controller* (computer with its supervisory program as represented by the pseudocode). The design method proceeds in the following order: (a) use the Build tool to describe and simulate the *plant* as a TTM object, (b) write the requirements in RTTL of how the *plant* should behave, (c) reverse engineer the proposed pseudocode *controller* into a TTM object, and (d) use the analysis tools to prove that the chart of the system under design (plant and controller) conforms to the requirements.

The order in which the design method proceeds can be justified by the following considerations. The plant is an already existing entity. Its behaviour is best described constructively using TTMs. Our main concern is that the plant behave safely and reliably no matter what controller is used. Hence, it is important to write the requirements with respect to the entities of the plant in an implementation free manner (using RTTL), before designing the controller. We can then try out the proposed pseudocode as a candidate controller, but we are free to select any controller that will meet the requirements. Since the proposed controller is to be implemented on a computer, it is also constructively described as a TTM.

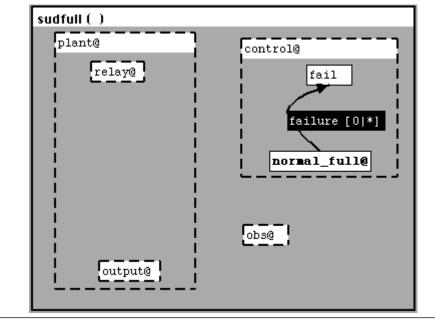

Before following the above design method step by step, we first give an overview of the complete system so that the reader will have an appreciation for the end product of the method. The chart for the system under design (Figure 5) is the AND-composition of the plant, controller and an "observer", i.e.

$$sud = plant \| control \| obs$$

(Eq 5)

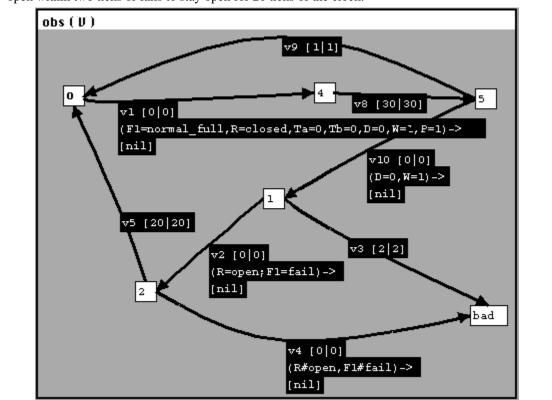

The observer (*obs*) watches the system for deficient behaviour without interfering with its operation (its use will be explained in Section 5.4 which deals with conformance testing). The relationship between the variables of the plant and controller are shown in Figure 6.

FIGURE 5. The TTMchart of the system under design (edit view)

#### sud = plant || control || obs

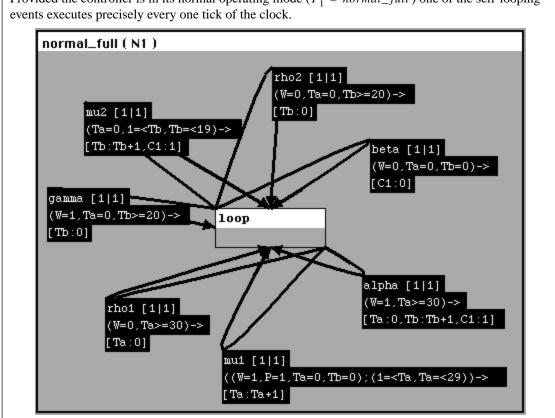

The object variable of *control* is  $F_1$  where  $type(F_1) = \{normal\_full, fail\}$ . See Figure 7 for further details of the plant. The internal structure of *normal\\_full* in the control chart is described in more detail in Figure 12.

FIGURE 6. Connection diagram for the system under design

## 5.1 Using the Build tool to describe the DRT plant

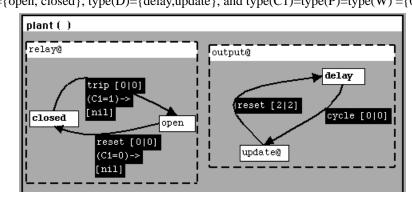

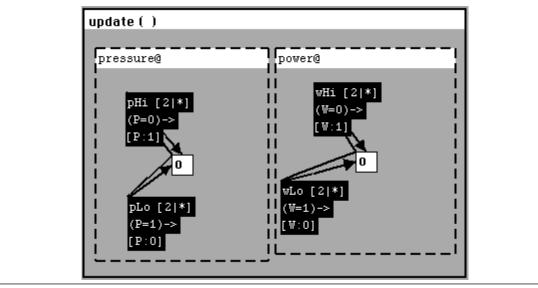

The *plant* object (Figure 7) is itself AND-composed of various sub-objects, i.e. plant = relay || output. The dashed lines in the edit view of the plant indicate that the *relay* object runs concurrently with the *output* object (AND-composition). The *relay* object can be in one of two control states closed or open called *activities*. Activities are the lowest level object (they have no internal structure). The *output* object

#### FIGURE 7. TTMchart description of the DRT plant

#### plant(C1;R,W,P,D)=relay(C1;R) || output(;D,P,W)

where R=relay position, C1=command to move relay, D=object variable of output, P=pressure and W=power.

The relay is opened (closed) immediately upon receiving the C1 command to do so. When D=delay, the last sensor updates have just been made and there are two ticks to the next change. type(R)={open, closed}, type(D)={delay,update}, and type(C1)=type(P)=type(W) ={0,1}

Zooming in to update@ produces the view below (P and W are updated every two ticks).

is XOR-decomposed into sub-objects *delay* and *update@*. The *update* object has further internal structure as indicated by the "@" suffix.

A structured object m, which is XOR-decomposed into sub-objects given by  $m_0, m_1, \ldots m_n$ , must have an associated *object variable*, and one of the sub-objects must be designated as the *default*. The default of m indicates where it begins executing when first entered, unless otherwise specified. For example, the *relay* object variable is R where type(R) = {closed, open}. The activity **closed** is the default (defaults are shown in bold in edit views). Hence initially (R = closed) is true.

The transitions in chart objects are called *events*, e.g. the events of the *relay* object are trip and reset. The events may test and set variables such as the input data variable C1 where type(C1) =  $\{0,1\}$ . The *guard* of the trip event is (C1=1); if the environment sets C1 the relay will trip thus initiating the shutdown process.

The Build tool translates each event of the various objects into transitions. For example, the transition relation associated with the trip event in *relay* is:

$$\rho_{trip}$$

:  $(R = closed) \land (C1 = 1) \land (R' = open) \land (\varepsilon' = trip)$

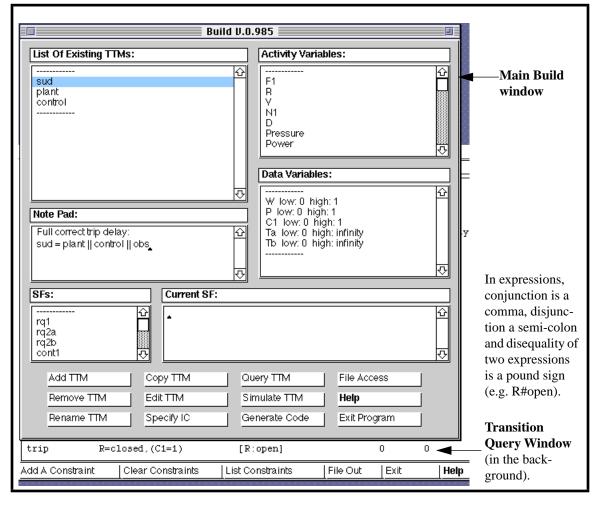

The main window of the Build tool (Figure 8) has a Query TTM button which

FIGURE 8. Main window of the Build tool

displays a list of the transitions in update format. The query window (behind the main window) shows that the enabling condition of trip is (R=closed, C1=1) and the lower and upper time bounds are zero (i.e. once the trip transition is enabled it is taken before the next tick of the clock).

The activities (lowest level objects) can themselves be given structure, in which case they also become sub-objects. For example, the *output* object is the XOR-composition of activity delay and sub-object *update@* (Figure 7). The "@" symbol at the end of an object name indicates that it has internal structure as shown in the second picture of Figure 7. The *update* object describes how the power (*W*) and pressure (*P*) sensor values may be updated every two ticks of the clock (thus capturing the assumption that signals are filtered). For example, the

spontaneous transition  $pHi[2,\infty]$  may set the power high after 2 clock ticks, after which the timed transition reset[2,2] forces the object out of the update mode.

The hierarchy for the plant objects is shown in Figure 9. The user can navigate

up and down the hierarchy from any level. At any point in the development, previously created charts can be imported as sub-objects, or existing objects can be refined by zooming in. There is no restriction on the number of levels or the type (AND or XOR) of sub-object that can be inserted at each level. The main window (Figure 8) can be used to enter initial conditions and to simulate the chart.

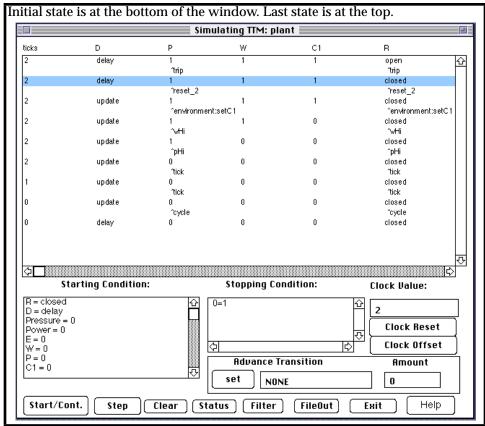

Figure 10 shows a computation of the plant in a simulation window. The computation starts with the cycle event which puts the plant into update mode. The last transition taken is trip which opens the relay (top of the screen). In between these two transitions, the clock ticks twice, the power and pressure go high and the trip transition is enabled and finally taken. For the computation shown in the figure, the environment sets the control value *C1* to open the relay at the appropriate time. However, there are also plant trajectories where the relay is not opened when it should be. For this reason, a controller is needed.

At certain points in the simulation, user input is required. For example, after two ticks of the clock, the user can nondeterministically choose whether to let the power or pressure go high, or whether to advance the clock.

Each time a new element is added to or deleted from the chart, the Build tool checks the syntactic correctness of the element. For example, data variables cannot be deleted if they are in use, the elements of types must be distinct, and expressions such as guards or updates must be correct. Events in a chart cannot have both their source and destination in parallel (AND-composed) objects.

FIGURE 10. Simulating the plant produces a computation

## 5.2 The DRT requirements

The informal requirements for the DRT (Section 2.0) must now be made precise. The first requirement may be written in real-time temporal logic (RTTL) as:

**R1:**

$$(bothHi \land \diamondsuit_{30}powerHi) \Rightarrow \diamondsuit_{[30, 32]} \square_{<20}(R = open)$$

(Eq. 6)

where the precise definitions of *bothHi*, *powerHi* are given below (Eq. 7). The above formula asserts that whenever a critical high is sensed, and 30 clock ticks later the power is still high, then the relay is opened within 32 ticks from the critical state and remains open until the 20th tick.

The actual system has a 3-microprocessor majority voting controller. For such systems we need to be able to express properties such as: "if at most one controller fails, the system will still satisfy its requirements", i.e. the above requirement becomes  $(\Box \neg fail) \rightarrow \mathbf{R1}$ . In the sequel we discuss a single microprocessor controller<sup>8</sup>, and refer the reader to the conference paper [38] on how the majority voting system can also be verified using compositional techniques and StateTime.

How should the predicates *bothHi* and *powerHi* be defined? The intuitively obvious definition *bothHi*  $\triangleq$  (*P* = 1  $\land$  *W* = 1) is not realizable by practical control-

**<sup>8</sup>**. The failure transition (see Figure 5) can be ignored for the single controller case as it is only needed for defining *fail* in the majority voting system.

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

lers because they cannot respond to instantaneous changes in the sensor values (the microprocessor described in Section 2.0 responds after one clock tick).

After an update, the *output* object (with object variable D) resides in activity delay. The clause (D = delay) can therefore be inserted as a conjunct of *bothHi*, thus indicating that the antecedent of (Eq. 6) is measured from a state from which the power and pressure remain constant for two clock ticks<sup>9</sup> (see Figure 7).

The controller cannot respond to a critical high if it is in the middle of counting its timeouts — thus the controller initial condition *init(control)* must also be a conjunct of *bothHi*. The correct definitions for the components of (Eq. 6) are thus given by:

$$bothHi \stackrel{\text{def}}{=} init(control) \land R = closed \land D = delay \land (P = 1 \land W = 1)$$

$$PowerHi \stackrel{\text{def}}{=} (D = delay \land W = 1)$$

(Eq. 7)

The state-formula *init(control)* cannot be fully specified until a proposed controller is suggested. For the controller of the next subsection, it is:

$$init(control) \stackrel{\text{def}}{=} (F_1 = normal\_full \land T_a = 0 \land T_b = 0)$$

(Eq 8)

Although the initialization of the controller cannot be fully specified until the controller is developed, we can nevertheless describe a "sanity check" that the state-formula *init(control)* must satisfy:

$$[\mathbf{R3}]: \neg init(control) \Rightarrow \diamondsuit_{\leq 52} init(control)$$

(Eq. 9)

[R3] requires that any controller must not deadlock under normal operation, i.e. must always return to its initial state after both timers have finished their count.

The second informal requirement for the DRT can be specified as:

**[R2]**:

$$powerLo \Rightarrow \diamondsuit_{\leq 2}(R = closed)$$

(Eq. 10)

where  $powerLo \triangleq (D = 0 \land W = 0) \land init(control)$ .

## 5.3 The DRT controller

In the previous subsections we showed how the plant can be described using TTMs and how the requirements can be specified in RTTL. The next phase involves designing the controller so that the system will conform to its requirements. In the case of the DRT, a candidate for the controller is already provided by the pseudocode (Figure 2), which is a loop that is executed every one tick of the clock. The pseudocode makes use of two integer counters *Ta* and *Tb* for the two time-outs of 30 and 20 clock ticks respectively.

When the original pseudocode (Figure 2) was translated into a TTM object, and composed together with the plant object, the Verify tool found that requirement [R1] failed to hold. On looking at the failing computation, it became obvious that the problem was due to the fact that the transition that opens the relay after counter *Ta* has timed out has an unnecessary dependence on the pressure. The sit-

A Visual Toolset for the Design of Real-Time Discrete Event Systems. December 2, 1996.

<sup>9.</sup> Alternatively, we can write  $\Box_{<2}(P = 1 \land W = 1)$  to indicate that the pressure and power must remain high for at least two clock ticks.

uation can be remedied by moving the "P=1 {pressure is high}" statement in the second line (Figure 2) to the fifth line (Figure 11).

| then | If counter Ta is reset then<br>If counter Tb is reset then<br>If <b>P=1 {pressure is high}</b> then<br>increment Ta {Transition : $\mu$ 1}<br>EndIf<br>Else<br>If counter Tb has timed out then<br>reset Tb {Transition : $\gamma$ }<br>Else<br>increment Tb<br>open Relay { <b>Transition:</b> $\mu$ 2}<br>Endif<br>Endif<br>Else<br>If counter Ta has timed out then<br>open Relay {Transition: $\alpha$ }<br>reset Ta<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Tb<br>Else<br>increment Ta {Transition : $\mu$ 1} | else | If counter Ta is reset then<br>If counter Tb is reset then<br>close Relay {Transition : ß}<br>Else<br>If counter Tb has timed out then<br>reset Tb {Transition : p2}<br>Else<br>increment Tb<br>open Relay { <b>Transition:</b> µ2}<br>Endif<br>Endif<br>Else<br>If counter Ta has timed out then<br>reset Ta {Transition : p1}<br>Else<br>increment Ta {Transition : µ1}<br>Endif |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

FIGURE 11. Corrected pseudocode for the computer to control the DRT

The TTM object corresponding to the corrected code is shown in Figure 12. Each time the microprocessor passes through the code it performs a group of operations (such as incrementing or resetting counters or opening and closing the relay). These operations define the update function of transitions. The lower and upper time bounds of each transition is 1, as the transition (if enabled) is performed exactly every 0.1 seconds.

The comments in the pseudocode (Figure 11) indicate how statements of the pseudocode are translated into the transitions of the TTM (Figure 12). The enabling condition for the transitions can be computed by taking the conjunction of the conditions specified by the relevant "If" statements. For example, the transition  $\mu_2$ , which is responsible for incrementing the counter  $T_b$  and opening the relay, has the update function [ $T_b$ : $T_b$  + 1,  $C_1$ :1]. Its enabling condition is computed as the disjunction of its occurrence in the *if-then* part of the main loop as well as its occurrence in the *else* part, i.e.

$$enb(\mu_2) \equiv (W = 1 \land T_a = 0 \land 1 \le T_b \le 19) \lor (W = 0 \land T_a = 0 \land 1 \le T_b \le 19)$$

$$\equiv (T_a = 0 \land 1 \le T_b \le 19)$$

The enabling condition can be trivially simplified to  $enb(\mu_2) \equiv (T_a = 0 \land 1 \le T_b \le 19)$  because  $type(W) = \{0, 1\}$ . The enabling condition of  $\mu_2$  is very different for the faulty code (Figure 2) and shows an unnecessary dependence on the pressure.

#### FIGURE 12. Result of transforming the controller pseudocode into a TTM

Provided the controller is in its normal operating mode ( $F_1 = normal_full$ ) one of the self-looping

## 5.4 Checking conformance

The main window of the Build tool (Figure 8) has a Generate Code button that can be used to translate the chart of the system under design into transition systems (as ASCII text files) that can be checked by the Verify and STeP tools. Both Verify and SteP take the text files directly as input.

The Verify tool found that the original pseudocode (Figure 2) did not meet the first requirement [R1]. The resulting counterexample was used to correct the code (Figure 11). The Verify tool was then used to show conformance of the corrected code, i.e. all three requirements [R1, R2 and R3] were shown to be valid. Using only the Verify tool the conformance check takes 35 minutes (Table 1).